# Application Note AN6002

# **APVSG Fast Control Port**

#### Purpose

For fast, time critical settings and data streaming the APVSG can be controlled over an additional port. This application note explains the configuration and usage of the Fast Control Port.

# **Table of Contents**

| Introduction                        | 2 |

|-------------------------------------|---|

| FCP Operation Modes                 | 2 |

| IQ Data Streaming with FCP          | 3 |

| Setup FCP for IQ Data Streaming     | 3 |

| Related SCPI Commands               | 3 |

| IQ Stream Timing                    | 1 |

| SCPI & FCP Example                  | 5 |

| FCP Input Delay Calibration         | 5 |

| Step by Step Guide for Calibration  | 5 |

| Required Signals during Calibration | 5 |

| Selecting Memory Segments           | 9 |

| Setup for Selecting Memory Segments | Э |

| FCP Segment SCPI Commands           | Э |

| Segment Stream Timing10             | ) |

| SCPI & FCP Example10                | ) |

| FCP Test Mode1                      | 1 |

| Related SCPI Commands1              | 1 |

| FCP IQ Stream in Test Mode1         | 1 |

| FCP Segment Stream in Test Mode1    | 3 |

| Cable Assembly14                    | 1 |

| Further Documentation14             | 1 |

# Introduction

The fast control port is a parallel port with the possibility for the user to control specific aspects of the IQ modulation of the APVSG. When activated, the FCP can be configured to operate in one of two main modes. The interface is set to stream either IQ data or memory segment IDs.

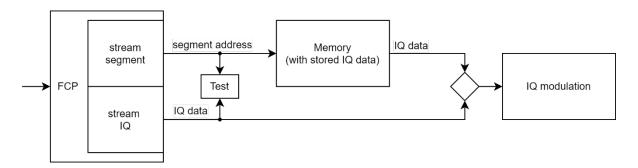

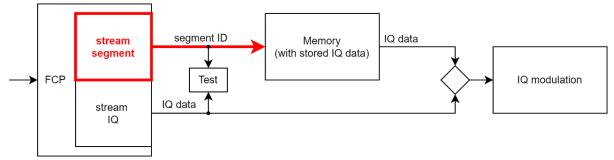

Setting the FCP in the former mode allows the user to stream IQ data to the APVSG directly and thus modulate the carrier frequency, as depicted in Figure 1. The FCP operates source synchronously and expects to receive IQ data in single data rate (SDR) along with a clock that runs at a stable, predefined rate. Depending on the FCP version and setting, the IQ modulation is read with a playback rate of 125 MSps or 250 MSps.

Instead of streaming the IQ modulation data directly through the FCP, the modulation data can also be replayed from the local APVSG IQ memory. When the FCP is configured in segment mode, it provides the option to choose the replayed IQ data. By streaming the memory segments IDs of the desired IQ data, the user is thus able to directly switch between the stored IQ data segments.

Figure 1: Functional diagram of FCP in APVSG with non-FCP parts omitted.

# **FCP Operation Modes**

The fast control port (FCP) supports two main use-cases:

- IQ Data streaming to the device for direct IQ modulation

- Segment ID streaming to select segments of the internal APVSG memory.

To select the operating direction of the Fast Control Port, the FCP must be configured with the following SCPI commands:

[:SOURce]:FCPort:STReam:SEGment OFF|ON|0|1

Sets the FCP to stream segment IDs.

[:SOURce]:FCPort:STReam:IQ OFF|ON|0|1

Sets the FCP to stream IQ data.

[:SOURce]:BB:ARBitrary:FCP:CLOC <freq>

Sets the FCP sampling and playback rate.

#### [:SOURce]:BB:ARBitrary:FCP[:STATe] OFF|ON|0|1

Sets the FCP as source for the IQ modulation.

Further related commands are documented in the Programmer's Manual[2] and application examples can be found on the following pages of this application note.

# **IQ Data Streaming with FCP**

The FCP can be set as an input for IQ modulation data which is then directly applied to modulate the carrier frequency. To configure the device to receive IQ data on the FCP, the FCP must be set into IQ streaming mode and the FCP must additionally be set as the source of the IQ modulation data.

The FCP for the source-synchronously clocked IQ streaming consists of 16 IQ-data bits, a valid bit, and a clock. The clock is a continuous signal at a fixed frequency with the valid bit and IQ data transmitted in single data rate (SDR). The FCP can operate at two different playback rates, namely

- 125 Mega samples per second with a continuous 250 MHz clock

- 250 Mega samples per second with a continuous 500 MHz clock

Please note that some devices only support the 125 MSps speed option for FCP. Please check the specifications for your device or ask your AnaPico representative for details hereof. Limitations and requirements:

- A stable frequency of 250 MHz/ 500 MHz is required on the clock pin of the FCP.

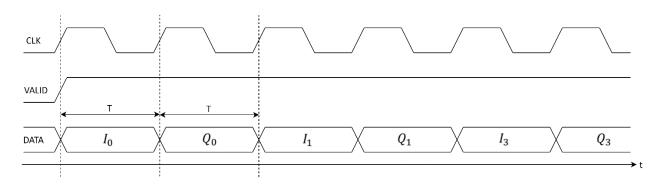

- Data at the FCP input must be streamed at 125 MSps or 250 MSps SDR. This is equivalent to the data bits toggling between I and Q every 4 ns/2 ns respectively. Please consult Figure 4 for a graphical representation.

- It is recommended to operate the sender (that drives the clock and the IQ data) and your APVSG at the same reference clock to avoid undesired frequency offset effects.

## Setup FCP for IQ Data Streaming

Configuration steps prior to transmission

- 1. Connect an external reference clock (recommended).

- 2. Connect the FCP input on the device.

- 3. Send stable 125 MHz/250 MHz clock signal on the FCP connector clock pins (see [1] for details on pin assignment)

Complete SCPI command sequence for IQ stream input on FCP:

| ROSC:EXT:FREQ <x></x>   | Sets the reference frequency (recommended)   |

|-------------------------|----------------------------------------------|

| ROSC:SOUR EXT           | Sets the reference to external (recommended) |

| FREQ <x></x>            | Sets initial RF output frequency             |

| OUTP:STAT <x></x>       | Sets RF output                               |

| BB:ARB:FCP:CLOC <x></x> | Sets the FCP playback rate                   |

| BB:ARB:FCP ON           | Sets FCP as source of the IQ modulation data |

| FCP:STR:IQ ON           | Sets FCP to IQ stream mode                   |

#### **Related SCPI Commands**

[:SOURce]:BB:ARB:FCP:CLOC <freq> This sets the FCP sampling and playback rate to <freq>. \*RST value: 125 MHz

## [:SOURce]:FCPort:STReam:IQ OFF|ON|0|1

Sets the FCP to stream IQ data.

\*RST value: OFF

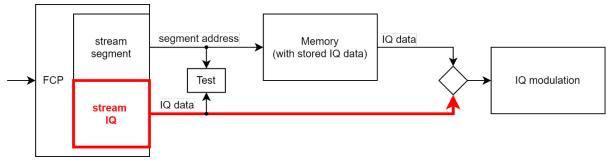

Figure 2: The FCP:STR:IQ SCPI command determines if the FCP is in IQ streaming mode. The received data is then forwarded to potentially modulate the carrier frequency. Note that this mode can only be enabled if all other FCP modes are disabled.

## [:SOURce]:BB:ARBitrary:FCP[:STATe] OFF|ON|0|1

Sets the FCP as the source of IQ modulation. \*RST value: OFF

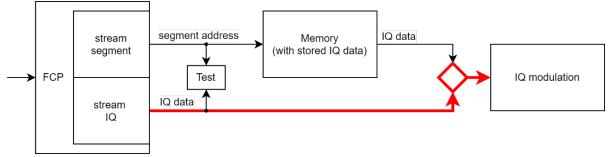

*Figure 3: The BB:ARB:FCP[:STAT] command decides if the FCP IQ data is forwarded for IQ modulation. This command only takes hold if the BB:ARB:WAV:STAT command is disabled.*

## **IQ Stream Timing**

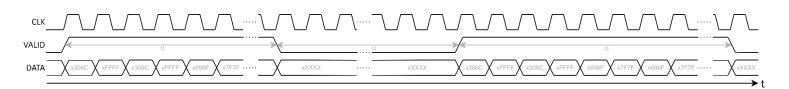

Figure 4: IQ stream input timing for the fast control port (FCP) with clock period  $T \in \{2ns, 4ns\}$

The FCP receives a valid signal that is synchronized with the first valid I-data sample, followed by the first Q-data sample. The valid signal should be driven low during the setup of the device to ensure proper sampling of I and Q data samples.

The phase relationship of input signals to the FCP are depicted in Figure 4. See [1] for details on pin assignment at the MDR 36-pin connector.

Clock and data edges are transferred at the same time. The FCP reads the data upon each rising edge of the clock. In order to optimize and relax the sampling of the IQ data, the input delay at the FCP should be calibrated before the first IQ transmission is started. The process and requirements for calibration are explained in section *FCP Input Delay* Calibration.

#### **SCPI & FCP Example**

This is a SCPI example to set the FCP. Make sure to follow the steps prior to transmission as described in section *Setup FCP for IQ Data Streaming*.

| ROSC:EXT:FREQ 10e6    | Sets the reference frequency to 10MHz        |

|-----------------------|----------------------------------------------|

| ROSC:SOUR EXT         | Sets the reference to external               |

| FREQ 50e6             | Sets initial RF output frequency 50 MHz      |

| OUTP:STAT ON          | Enables RF output                            |

| BB:ARB:FCP:CLOC 125e6 | Sets the FCP playback rate to 125 MHz        |

| FCP:STR:IQ ON         | Sets FCP to IQ stream mode                   |

| BB:ARB:FCP ON         | Sets FCP as source of the IQ modulation data |

After successfully configuring the device, the IQ modulation data (e.g. a 1-tone) can be sent to the FCP - make sure the valid signal is synchronized to the first 16-bit I-data sample. A valid input IQ stream results in a modulated carrier frequency at the RF output. You can now

- Set some frequency with FREQ <x>.

- Send another IQ modulation e.g. 2-tone to the FCP input.

- Watch the output being modulated.

If you have trouble setting up the FCP to correctly receive your IQ data, have a look at section *FCP Test Mode*. The FCP IQ streaming comes with an integrated testing mode that can help detect the most common issues in your setup.

#### **FCP Input Delay Calibration**

The FCP has a built-in opportunity to calibrate the input delay for the data ports relative to the clock port. This feature allows the user to account for signal delays that occur between the different fast control port pins and thereby optimize the timing of the captured signals. This optimization is done automatically with a calibration procedure that will be explained hereafter. During the calibration process, the FCP input delay of each data bit is adjusted individually.

## **Step by Step Guide for Calibration**

- 1. Start up the device

- 2. Physically connect an external reference clock to the APVSG device

- 3. Lock to the external reference

- a. SCPI commands

ROSC:EXT:FREQ <freq>set the external reference frequencyROSC:SOUR EXTset the reference clock source to external

- b. or use the reference clock tab in the APVSG GUI

- 4. Physically connect the FCP cable

- 5. Send a stable input on the FCP

- a. Stable clock signal of 250 or 500 MHz depending on playback rate

- b. Keep valid signal low

- c. Data input: any arbitrary 16-bit signal

- 6. Configure the FCP for IQ streaming

- a. SCPI commands

| BB:ARB:FCP:CLOC <freq></freq> | set the FCP playback rate (125 or 250MHz) |

|-------------------------------|-------------------------------------------|

| BB:ARB:FCP ON                 | set the FCP as source for IQ modulation   |

| FCP:STR:IQ ON                 | enable FCP for IQ streaming               |

|                               |                                           |

- b. Or use the APVSG GUI to set the device into FCP IQ streaming mode

- 7. Send the required calibration signals (see below for details) on the FCP input port

- 8. Start the calibration

- a. SCPI command

FCP:STR:CAL 0 start the calibration

The calibration will take several minutes to complete. Please do not modify or disturb the setup during this process.

## **Required Signals during Calibration**

The same LFSR pattern that is used for the FCP tests is also deployed for the calibration (see section *FCP IQ Stream in Test Mode* for related information). To calibrate the FCP input with your existing setup, please make sure you meet the following requirements for the signals at the FCP interface.

- Stable clock on FCP clock pin

- Source synchronous transmission

- Pseudo-random pattern at IQ data pins

- Signal at valid pin toggling every 2.5-3 seconds

- Min. 200 valid-high periods

- FCP input signals use the same reference clock as the APVSG

#### Stable Clock

The input signal of the clock pin needs to be a stable 250 MHz or 500 MHz, depending on which playback you are intending to use the FCP with. If you would like to use both the 125 MSps and the 250 MSps playback rates, please either do a new calibration whenever you switch the playback rate or calibrate your FCP input with the faster playback rate. You need to drive

- A stable 250 MHz at the clock pin for FCP with 125 MSps playback rate or

- A stable 500 MHz at the clock pin for FCP with 250 MSps playback rate.

For a proper calibration setup, please make sure the clock signal on the FCP input is generated with the same reference clock as the reference clock for the APVSG. Using an external reference clock is always recommended for streaming IQ data to the FCP.

#### Pattern for IQ Data

The IQ data pins of the FCP need to be driven with a predefined pseudo random pattern. See [1] for information on pin assignment on the fast control port.

The required I and Q data pattern can be generated with linear feedback shift registers (LFSR). The following code example describes how the I and Q data are generated.

```

// initialize I and Q

i_0 = 0x306C;

q_0 = 0xFFFF;

do { // for each iteration.

i = i XOR (i << 7);

i = i XOR (i >> 9);

i = i XOR (i << 8);

q = q XOR (q << 7);

q = q XOR (q << 8);

q = q XOR (q << 8);

}</pre>

```

• For calibration with a 125 MSps playback rate, the I and Q data samples are sent alternatingly, with each new IQ pair representing a new iteration in the above code example. This will result in a pattern like

| $i_0 = x306C$ | $q_0 = xFFFF$ |

|---------------|---------------|

| i_1 = x696F   | $q_1 = x7F7F$ |

| $i_2 = x5E80$ | $q_2 = x5F9F$ |

and so forth. Figure 5 depicts how the I and Q data should be sent consecutively. Please make sure there is a new data sample at every rising clock edge. The data sample that arrives along with any rising edge of the valid bit must be an I data sample – not a Q data sample. However, this data sample does not necessarily have to be the  $i_0$  sample. It can be any  $i_n$  sample if the consecutive data sample is the corresponding  $q_n$  sample.

• The order of I and Q samples needs to be changed slightly for calibration with a playback rate of 250 MSps. The sender must generate two pairs of IQ data samples as described in the above code example. The pairs are then sent to the FCP successively. Figure 6 depicts the order of the required IQ data which is

| i 0 = x306C   | q 0 = xFFFF   | i 0 = x306C   | q 0 = xFFFF   |

|---------------|---------------|---------------|---------------|

| i_1 = x696F   | $q_1 = x7F7F$ | i_1 = x696F   | $q_1 = x7F7F$ |

| $i_2 = x5E80$ | $q_2 = x5F9F$ | $i_2 = x5E80$ | $q_2 = x5F9F$ |

Similar to the slower playback rate, a I data sample must be sent along with a rising edge of the valid signal.

While the valid signal is low, the 16 data pins can be driven with any arbitrary signal. The data input will thence be considered invalid and inconsequential for calibration.

#### Valid Signal

The signal at the valid pin of the FCP (see [1] for details on pin mapping) must stay low while the FCP is being enabled. In Figure 5 and Figure 6 the time periods for which the valid signal is high or low are labeled  $t_1$  and  $t_2$  respectively. For calibration, these periods are required to be roughly 3 seconds.

#### $t_1, t_2 \in [2.3 \, s, 3.5 \, s]$

For one whole calibration to finish, the valid bit must rise from low to high approximately 200 times.

#### **Reference Clock**

It is recommended to have a reference clock that drives both the APVSG as an external reference and all the signals generated by the sender of all the FCP signals. If the reference clock is not locked to both the sender and the APVSG, the FCP input calibration may fail due to frequency offset effects that can not be circumvented.

#### **Required FCP Signals**

The following figures each show an example of the signals required at the FCP pins during calibration. All signals are explained separately and in detail in the preceding subsections.

Figure 5: FCP signals for calibration with 125 MSps playback rate and 250 MHz clock. Figure not to scale.

Figure 6: FCP signals for calibration with 250 MSps playback rate and 500 MHz clock. Figure not to scale.

# **Selecting Memory Segments**

The fast control port (FCP) can be configured to receive memory segment IDs to select desired memory segments for playback. When the FCP is configured in segment selection mode, the FCP cannot be configured to run in any other mode simultaneously. The FCP expects a 16-bit wide memory segment ID, as well as a valid signal that indicates when a new ID is valid at the FCP.

#### **Setup for Selecting Memory Segments**

The configuration steps for segment streaming to FCP are straight forward.

- Connect the FCP input at the connector on the APVSG. See [1] for pin assignment on the FCP connector.

- 2. Set the FCP to Segment ID stream mode with the SCPI command **FCP:STR:SEG ON**

#### **FCP Segment SCPI Commands**

#### [:SOURce]:FCPort:STReam:SEGment OFF|ON|0|1

Sets the FCP to stream segments IDs. \*RST value: OFF

Figure 7: The FCPort:STReam:SEGment command determines whether the FCP is streaming memory segment IDs. Note that this mode can only be enabled if all other FCP modes (e.g. stream IQ) are turned off.

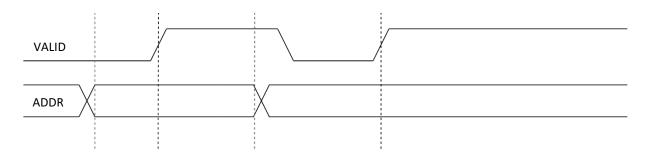

## Segment Stream Timing

The FCP receives a valid signal that is synchronized with the data. Each new segment ID needs to be accompanied by a rising edge of the valid signal. The valid signal should be driven low during the setup of the APVSG.

The temporal relationships of the input signals to the FCP are depicted in Figure 4. See [1] for details on pin assignment at the connector.

Segment IDs and valid bit edges are transferred at the same time. The FCP reads the input with a sampling rate of 250 Mb per second for each signal which naturally limits the switching of the valid signal to every 4 ns the earliest.

Figure 8: Timing diagram for memory segment inputs (not to scale)

#### **SCPI & FCP Example**

- 1. Write some IQ data to the internal memory of the APVSG, e.g. a 1-tone modulation. This can be done by e.g. uploading the data of a QI file with the APVSG GUI.

- 2. You can use either the GUI or the following SCPI commands to further setup the APVSG.

| FREQ 50e6                 | Sets initial RF output frequency 50 MHz      |

|---------------------------|----------------------------------------------|

| OUTP:STAT ON              | Enables RF output                            |

| BB:ARB:WSEG:SOUR FCP      | Sets FCP as source for segment selection     |

| FCP:STR:SEG ON            | Sets FCP to segment stream mode              |

| <b>BB:ARB:WAV:STAT ON</b> | Sets RAM as source of the IQ modulation data |

After successfully configuring the device, the segment ID can be sent to the FCP - make sure the positive edge of your valid signal is sent along with the 16-bit segment ID signal. You can now

- Set some frequency with FREQ <x> on the APVSG.

- Send a different segment ID with a new positive edge on the valid signal to switch the IQ modulation data replayed from the RAM.

[Note: The device needs to have stored a waveform with the designated ID you are sending on FCP, or there will be no modulation waveform to be replayed.]

- Watch the output being modulated accordingly.

# **FCP Test Mode**

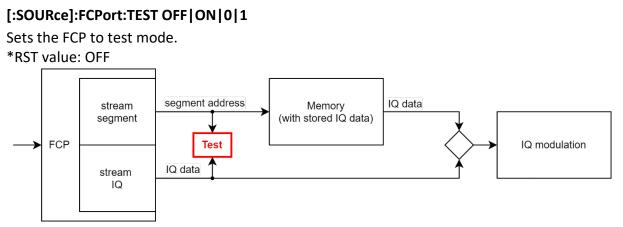

The following sections describe the behavior of the FCP in test mode. For each streaming mode of the FCP the functionality of the test varies to account for the type of transmission employed in the specific streaming mode.

There are two SCPI commands for FCP testing. One command to enable or disable the test mode for FCP and a second command to print the related information on the active FCP streaming mode and the testing of this mode.

## **Related SCPI Commands**

Figure 9: The FCP:TEST command dictates if the FCP is being run in test mode. Please note that the behavior of the FCP test depends on the applied streaming mode at any given time.

## [:SOURce]:FCPort:DIAGnostic

Gets diagnostic information regarding the FCP.

#### [:SOURce]:FCPort:DIAGnostic?

Prints the previously gathered diagnostic information of the FCP.

The displayed information varies according to streaming mode. When the FCP test mode is activated, the test information and results are show along with the diagnostic information on the current FCP state.

#### FCP IQ Stream in Test Mode

The diagnostic information for the FCP relays the state of the received clock on FCP. For the FCP to be able to sample the IQ data correctly in IQ streaming mode, the respective clock pin must be driven with a stable clock signal with 50% duty cycle. The FCP will only be able to lock onto the clock signal if it is stable. Consult the FCP:DIAG SCPI command to check if your applied clock signal meets these requirements. Please note, that it is recommended to drive this clock signal and the reference clock for the APVSG with the same source clock to avoid undesired frequency offset effects.

Once a sufficient clock signal is applied, the IQ data can be tested for correct transmission. The FCP IQ stream mode contains a built-in test that makes use of a linear feedback shift register (LFSR) to generate a pseudo-random test pattern for the I-data and the Q-data separately. Thus, all combinations of the 16-bit IQ data are tested except for the 0x0000 combination. In the following, the iterations to generate the test pattern are described in pseudo code.

```

// initialize I and Q

i_0 = 0x306C;

q_0 = 0xFFFF;

do { // for each iteration.

i = i XOR (i << 7);

i = i XOR (i >> 9);

i = i XOR (i << 8);

q = q XOR (q << 7);

q = q XOR (q << 8);

q = q XOR (q << 8);

}</pre>

```

Which will result in:

$I_0 = 0x306C, Q_0 = 0xFFFF, I_1 = 0x696F, Q_1 = 0x7F7F, I_2 = 0x5E80, Q_2 = 0x5F9F, ...$

The built-in comparator will wait for the initial pattern of  $I_0$  and  $Q_0$  to start comparing the received data. Make sure the valid bit you send to the FCP is high during the transmission of the test patterns or the FCP will not recognize the data as valid input. Also take care to send the rising edge of the valid bit simultaneously with an I-data as described in section *IQ Stream Timing.*

The comparator will then compare the data on the FCP input while it is valid and count the numbers of errors detected for each bit. The pattern comparison will stop if the valid bit is low and resume when it is high again. The diagnostic information of the FCP that can be accessed with the FCP:DIAG command gives information on the state of the valid signal, the test comparison and the amounted errors. The displayed number of errors per bit are limited to  $2^{21}$  and will overflow if excessed. Furthermore, the presented values do not necessarily represent an exact point in time since the error counts for the separate bits are gathered consecutively and not simultaneously.

Example of a possible FCP:DIAG response:

```

****** FCP diagnostic:

FCP State : IQ Stream (Slave)

FCP clock : locked and frequency OK

FCP Data : valid

FCP Test : enabled

Test State: comparing patterns

Current error count of each bit:

D15: D14: D13: D12: D11:

D10:

D09:

D08:

0

0

0

0

0

0

0

0

_____

___

D07: D06: D05: D04: D03: D02: D01:

D00:

0

0 0 0 0

0

0

0

```

#### **FCP Segment Stream in Test Mode**

The test mode for memory segment address stream is a lot simpler than for the IQ streaming mode. Since the transmission is not source synchronous but the data is sampled at the FCP input, there is only diagnostic information about the valid bit and the received address.

In test mode, the address input is directly forwarded to the diagnostic information along with the state of the valid bit.

Example of a possible FCP:DIAG command response:

\*\*\*\*\*\* FCP diagnostic:

FCP State : Segment Stream (Slave) FCP ready : 1 FCP Test : enabled FCP Data : valid FCP Input : 0x0004;

# **Cable Assembly**

The specifications for the connecting cable on the FCP port vary depending on the deployed use-case of the FCP. For recommendations on parts for a custom cable for either IQ streaming or segment address streaming, please contact your AnaPico representative directly.

# **Further Documentation**

- [1] Data Sheet APVSG https://www.anapico.com/downloads/catalog-and-data-sheets/

- [2] AnaPico Programmer's Manual for Signal Generators https://www.anapico.com/downloads/manuals/

- [3] AN6003 APVSG Memory Segmentation https://www.anapico.com/downloads/application-notes-and-videos/